【专利解密】东科半导体改进芯片硬宏供电结构

【嘉德点评】东科半导体的芯片硬宏供电专利,针对了现有供电网络结构的缺陷,提出了一种提升芯片硬宏供电可靠性的方法,通过在硬宏上方位置芯片内部构建硬宏专用电源网络,来提升芯片硬宏供电可靠性。

集微网消息,在国内芯片设计绿色化、低功耗的发展趋势下,许多公司大力投入进行技术积累。东科半导体是我国主要从事高效绿色电源IC和大功率电源IC设计、生产和销售的企业,其同步整流芯片使用了全球首创的独特“两引脚”封装技术,供电稳定性高,市场竞争优势强。

宏单元是集成电路(IC)设计中常见的单元,而硬宏则为特定的功能模块,包括存储器、锁相环PLL等各种IP核,可作为专用集成电路的功能模块。在硬宏的电源设计中,通常使用芯片本身的电源网络平铺在整个芯片进行供电,并通过叠层孔与其供电引脚连通。然而这种供电网络结构的鲁棒性较差,在特殊或极端条件下,供电可靠性无法得到保障,可能会芯片性能。

基于这一背景,东科半导体于2020年5月9日提供了一项名为“一种提升芯片硬宏供电可靠性的方法”(申请号:202010388483.2)的发明专利,申请人为安徽省东科半导体有限公司。

在芯片设计中,硬宏单元的逻辑在内部已经集成好,因此可能会存在没有芯片电源网络的金属层。本发明则提供了一种提升芯片硬宏供电可靠性的方法,在不增加芯片面积的情况下,充分利用硬宏上方空置的几层金属层提升供电可靠性。

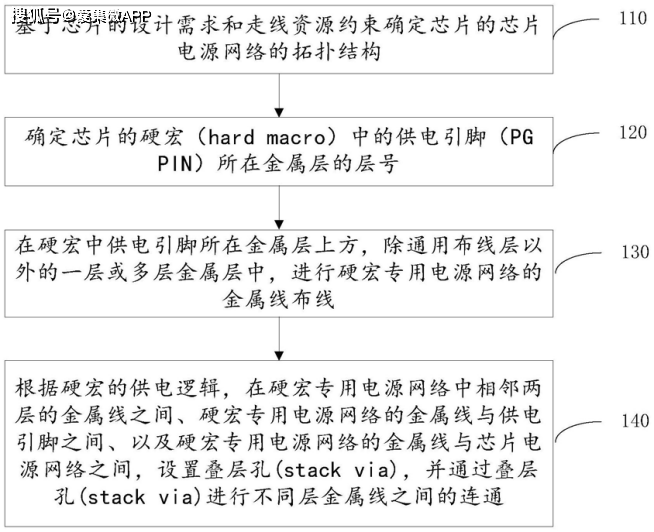

图1 提升芯片硬宏供电可靠性的方法流程图

参考图1,该专利提出的提升硬宏供电可靠性的方法主要包括4个步骤,首先基于芯片的设计需求和走线资源约束确定芯片电源网络的拓扑结构(步骤110),包括金属层数、通用布线层数、等。紧接着确定芯片硬宏中的供电引脚所在金属层的层号(步骤120)。

在硬宏中供电引脚所在金属层上方,除通用布线层以外的一层或多层金属层中,进行硬宏专用电源网络的金属线布线(步骤130),具体可表现为选定金属层用于电源网络的布线,并确定走线轨道,划分为多个布线单元等。最后根据硬宏的供电逻辑,在硬宏专用电源网络中相邻两层的金属线之间、金属线与供电引脚之间、以及金属线与芯片电源网络之间,设置叠层孔,并通过叠层孔进行不同层金属线之间的连通(步骤140)。

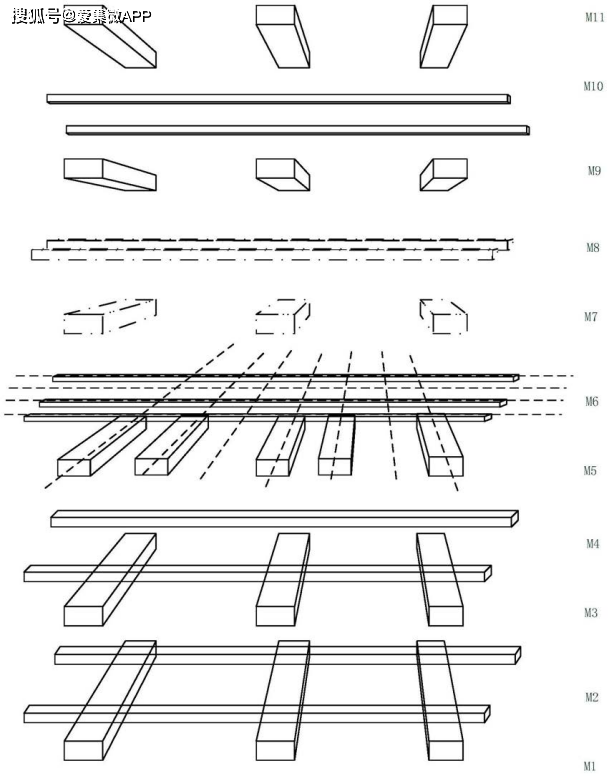

图2 芯片电源网络的拓扑结构示意图

图2是本专利提出的一种芯片电源网络拓扑结构图,展示了一个具体的提升芯片硬宏供电可靠性的方法过程示意图。首先从M1到M11的金属线依次沿纵向、横向、纵向、横向…… 方向排布。选定金属层M5、M6用于硬宏专用电源网络的金属线布线,走线轨道如图中虚直线所示,选择其中两条走线轨道用于金属线布线。图中清晰展示了布线后的M5、M6上的金属线长方形框体,而M7、M8在硬宏对应位置上没有金属线。

简而言之,东科半导体的芯片硬宏供电网络专利,针对了现有供电网络结构的缺陷,提供了一种提升芯片硬宏供电可靠性的方法,通过在硬宏上方位置芯片内部构建硬宏专用电源网络,来提升芯片硬宏供电可靠性。

东科半导体是我国芯片生产和封装的重要,在现有的市场和技术基础之上,积极融资并投入研发,提升芯片品质,相信未来东科能够越做越强,引领提升国内半导体产业水平。

(校对/holly)

责任编辑: